加强ESD保护的提示

发布时间:2025-07-21 10:06

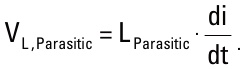

1介绍今天,使用小于130 nm的高级技术开发了现代电子产品中的许多芯片组,从LCD电视到手机。这些技术对超过3.3V的直流电压的容忍度极低,因此静电释放脉冲可能会影响此类设备上的灾难。此外,对“车载”或“交易板” ESD保护的要求减少到500 V,低于通常的现场要求8 kV。本文介绍了董事会设计师可以用来帮助设计师达到设计的ESD水平的各种方法,当所选的ESD保护设备未能通过ESD系统时。董事会设计人员不仅需要外部静电排放的外部保护,而且还需要在小几何形状中考虑芯片组的弱点,以确保其坚固耐用。如上一篇论文所述,在受保护的数据线上或I/或PIN的8 kV额定ESD设备的位置不能保证芯片组本身在系统内测试中通过8 kV。通常,ESD设备本身不会提供足够的保护,这可能导致过早的芯片组故障。本文列出了一些指南原则,以提供设计人员加强ESD保护的参考。 2设备的位置和布局对于使ESD保护器的有效性最大化很重要。为此,设计师最能知道各种寄生电感器对董事会的影响。 The specialAttention is the inductor, as a spike voltage of 30 V develops in the PCB line by only 1 nh of 8 kV ESD shock (i.e. 30 a): Note: This discussion assumes that all threats to the ESD enter the system through ports in Figure 1. Figure 1 Four parasitic inductors need to be used of the ESD device, the four parasite indeson, which LESD, Lesh, Lesh, Lesh, should consider the LGND,LIC和LPORT。图1显示了它们的位置。 LESD和LGND具有增加电压Of夹具(或VIC),而LIC和LPORT则从设计师中受益。让我们先看看两个有害电感器。 3 LESD和LGND有时,板布局不允许将ESD设备直接放在PCB电路上。因素有所不同,但最终,远离受保护数据线的一厘米远的位置可以迅速转换为大约十伏。 GND巴士也是如此。在某些设计中,ESD设备的GND必须经过许多孔,甚至穿过通道到达GND平面。除了流入ESD设备的当前ESD产生的电压外,这两个电感器还形成电压尖峰(即iPeak * rdynamic)。以下简化的示例描述了LESD和LGND对VIC的影响。在提供一个示例之前,我们需要指出,常见的PCB制造过程可以为典型的微带痕迹提供约3 nh/cm(考虑到一定宽度,厚度和介电介质,是一样的)。它的连接,让我们假设在此示例中假设8 kV的ESD脉冲和一个动态电阻为1Ω的ESD设备。此外,让我们看一下两个不同的布局,布局A和布局B,即Lesd = LGND = 1.5 nh(每个0.5 cm)和Lesd = lgnd = 3.0 NH(每个1.0厘米)。因此,通过将痕量长度(即LESD和LGND)从0.5 cm增加到1厘米,VIC可以增加75%。图2显示了布局B和与每个组件关联的电压。图2相关电压中的布局B(例如4 LIC和许多ESD设备数据板中的LOTP),通常解释说,该设备将尽可能接近输入ESD。其目的是使LPOR比率尽可能少(即LIC LPORT)。放松电感不一定会影响ESD的整体性能,而是LIC的电感。 LIC的不平等将是通过提供大电压倒塌的ESD脉冲初始峰值电流的延伸“朝向”组合电路。随着电感器的降低(即,ESD设备更接近集成电路),电压塌陷继续降低,直到未产生其他优势为止。因此,设计师最好以LIC比率尽可能少地利用PCB电路的寄生特性。图3显示了我们指的电压塌陷。图3集成电路电压的崩溃图4 ESD设备和受保护的集成电路共享使用LIC和LOTP的静电脉冲的当前加载是提高ESD整体性能的直接方法。但是,无论上述比例如何,有些设计最初都失败了。换句话说,LIC的量不能为ESD峰值电流提供足够的缓冲。 5个缓冲电阻一次,上述技术不足以为特定电路板设计提供最大的ESD保护。原因是电流ESD的“片上”结构太高,导致I/O短暂旋转GND或VCC并损坏。图4显示,ESD设备和受保护的集成电路确实共享了ESD脉冲的当前加载,这有助于清楚地说明问题。该图(减去迹线的电感)显示了静电放电的正脉冲,其中保护装置带有大部分电流,但本质上是带有集成电路的电阻电压分离器。 。如图4所示,集成电路的铁路负责将剩余的电流或“离开”电流引导到VCC(通常由旁路电容器返回GND)。很难确定集成电路ESD保护的相应电阻是什么,但毫无疑问,它比车载ESD设备高。例如,如果片上保护器(RCHIP)外部ESD防御者的阻力为1ΩESD防御者为1Ω,集成电路的峰值电流为:为了减小当前流入集成电路的峰,对串联电路的阻力可以集成电路。图5如图5所示。图5在外部ESTRATED电路之间显示电阻,如图5.图5中的外部电路5.当前的外部电路和图5。可以减少近50%(在这种情况下)。显然,电阻量可以增加超过10Ω以进一步减少当前泄漏,最大电阻量通常取决于特定的应用情况。还应注意,当在HDMI和USB 3.0等某些高速应用中使用该技术时,应格外小心。 rbuffer电阻会干扰线阻抗,导致信号超过规格Of遵守相同的标准,但是仔细的董事会设计可以支付任何不利影响。但是,董事会设计人员必须在工具箱中维护该技术,并在板上或系统的ESD级别低于要求时将其应用。 6结论如今,现代芯片组比以往任何时候都更容易受到ESD瞬变的影响。多亏了小的几何技术,这些集成的电路需要坚固的外部ESD解决方案才能承受测试ESD。本文提供了董事会设计师可以用来优化ESD解决方案的四种技术或技术。 ●减少“存根”或LESD的长度; ●减少GND的长度和/或用于减少LGND的VIA的数量; ●在给定设计中,使LIC比率尽可能少; ●如果上面的项目1-3不足,请在ESD设备和集成电路之间使用缓冲电阻。所有这些技能均设计为Upang降低集成电路的电压,并限制当前的电路D可以通过片上ESD结构来处理。通过遵循这些简单的规则,董事会设计师可以获得超过行业标准的更强大的ESD解决方案。

1介绍今天,使用小于130 nm的高级技术开发了现代电子产品中的许多芯片组,从LCD电视到手机。这些技术对超过3.3V的直流电压的容忍度极低,因此静电释放脉冲可能会影响此类设备上的灾难。此外,对“车载”或“交易板” ESD保护的要求减少到500 V,低于通常的现场要求8 kV。本文介绍了董事会设计师可以用来帮助设计师达到设计的ESD水平的各种方法,当所选的ESD保护设备未能通过ESD系统时。董事会设计人员不仅需要外部静电排放的外部保护,而且还需要在小几何形状中考虑芯片组的弱点,以确保其坚固耐用。如上一篇论文所述,在受保护的数据线上或I/或PIN的8 kV额定ESD设备的位置不能保证芯片组本身在系统内测试中通过8 kV。通常,ESD设备本身不会提供足够的保护,这可能导致过早的芯片组故障。本文列出了一些指南原则,以提供设计人员加强ESD保护的参考。 2设备的位置和布局对于使ESD保护器的有效性最大化很重要。为此,设计师最能知道各种寄生电感器对董事会的影响。 The specialAttention is the inductor, as a spike voltage of 30 V develops in the PCB line by only 1 nh of 8 kV ESD shock (i.e. 30 a): Note: This discussion assumes that all threats to the ESD enter the system through ports in Figure 1. Figure 1 Four parasitic inductors need to be used of the ESD device, the four parasite indeson, which LESD, Lesh, Lesh, Lesh, should consider the LGND,LIC和LPORT。图1显示了它们的位置。 LESD和LGND具有增加电压Of夹具(或VIC),而LIC和LPORT则从设计师中受益。让我们先看看两个有害电感器。 3 LESD和LGND有时,板布局不允许将ESD设备直接放在PCB电路上。因素有所不同,但最终,远离受保护数据线的一厘米远的位置可以迅速转换为大约十伏。 GND巴士也是如此。在某些设计中,ESD设备的GND必须经过许多孔,甚至穿过通道到达GND平面。除了流入ESD设备的当前ESD产生的电压外,这两个电感器还形成电压尖峰(即iPeak * rdynamic)。以下简化的示例描述了LESD和LGND对VIC的影响。在提供一个示例之前,我们需要指出,常见的PCB制造过程可以为典型的微带痕迹提供约3 nh/cm(考虑到一定宽度,厚度和介电介质,是一样的)。它的连接,让我们假设在此示例中假设8 kV的ESD脉冲和一个动态电阻为1Ω的ESD设备。此外,让我们看一下两个不同的布局,布局A和布局B,即Lesd = LGND = 1.5 nh(每个0.5 cm)和Lesd = lgnd = 3.0 NH(每个1.0厘米)。因此,通过将痕量长度(即LESD和LGND)从0.5 cm增加到1厘米,VIC可以增加75%。图2显示了布局B和与每个组件关联的电压。图2相关电压中的布局B(例如4 LIC和许多ESD设备数据板中的LOTP),通常解释说,该设备将尽可能接近输入ESD。其目的是使LPOR比率尽可能少(即LIC LPORT)。放松电感不一定会影响ESD的整体性能,而是LIC的电感。 LIC的不平等将是通过提供大电压倒塌的ESD脉冲初始峰值电流的延伸“朝向”组合电路。随着电感器的降低(即,ESD设备更接近集成电路),电压塌陷继续降低,直到未产生其他优势为止。因此,设计师最好以LIC比率尽可能少地利用PCB电路的寄生特性。图3显示了我们指的电压塌陷。图3集成电路电压的崩溃图4 ESD设备和受保护的集成电路共享使用LIC和LOTP的静电脉冲的当前加载是提高ESD整体性能的直接方法。但是,无论上述比例如何,有些设计最初都失败了。换句话说,LIC的量不能为ESD峰值电流提供足够的缓冲。 5个缓冲电阻一次,上述技术不足以为特定电路板设计提供最大的ESD保护。原因是电流ESD的“片上”结构太高,导致I/O短暂旋转GND或VCC并损坏。图4显示,ESD设备和受保护的集成电路确实共享了ESD脉冲的当前加载,这有助于清楚地说明问题。该图(减去迹线的电感)显示了静电放电的正脉冲,其中保护装置带有大部分电流,但本质上是带有集成电路的电阻电压分离器。 。如图4所示,集成电路的铁路负责将剩余的电流或“离开”电流引导到VCC(通常由旁路电容器返回GND)。很难确定集成电路ESD保护的相应电阻是什么,但毫无疑问,它比车载ESD设备高。例如,如果片上保护器(RCHIP)外部ESD防御者的阻力为1ΩESD防御者为1Ω,集成电路的峰值电流为:为了减小当前流入集成电路的峰,对串联电路的阻力可以集成电路。图5如图5所示。图5在外部ESTRATED电路之间显示电阻,如图5.图5中的外部电路5.当前的外部电路和图5。可以减少近50%(在这种情况下)。显然,电阻量可以增加超过10Ω以进一步减少当前泄漏,最大电阻量通常取决于特定的应用情况。还应注意,当在HDMI和USB 3.0等某些高速应用中使用该技术时,应格外小心。 rbuffer电阻会干扰线阻抗,导致信号超过规格Of遵守相同的标准,但是仔细的董事会设计可以支付任何不利影响。但是,董事会设计人员必须在工具箱中维护该技术,并在板上或系统的ESD级别低于要求时将其应用。 6结论如今,现代芯片组比以往任何时候都更容易受到ESD瞬变的影响。多亏了小的几何技术,这些集成的电路需要坚固的外部ESD解决方案才能承受测试ESD。本文提供了董事会设计师可以用来优化ESD解决方案的四种技术或技术。 ●减少“存根”或LESD的长度; ●减少GND的长度和/或用于减少LGND的VIA的数量; ●在给定设计中,使LIC比率尽可能少; ●如果上面的项目1-3不足,请在ESD设备和集成电路之间使用缓冲电阻。所有这些技能均设计为Upang降低集成电路的电压,并限制当前的电路D可以通过片上ESD结构来处理。通过遵循这些简单的规则,董事会设计师可以获得超过行业标准的更强大的ESD解决方案。